Universidade Estadual de Campinas Instituto de Computação

## Armando Faz Hernandez

## High-Performance Elliptic Curve Cryptography: A SIMD Approach to Modern Curves

Criptografia de Curvas Elípticas de Alto Desempenho: Uma Abordagem SIMD para Curvas Modernas

> CAMPINAS 2022

### Armando Faz Hernandez

## High-Performance Elliptic Curve Cryptography: A SIMD Approach to Modern Curves

## Criptografia de Curvas Elípticas de Alto Desempenho: Uma Abordagem SIMD para Curvas Modernas

Tese apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Doutor em Ciência da Computação.

Thesis presented to the Institute of Computing of the University of Campinas in partial fulfillment of the requirements for the degree of Doctor in Computer Science.

#### Supervisor/Orientador: Prof. Dr. Julio Cesar Lopez Hernandez

Este exemplar corresponde à versão final da Tese defendida por Armando Faz Hernandez e orientada pelo Prof. Dr. Julio Cesar Lopez Hernandez.

CAMPINAS 2022

#### Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Ana Regina Machado - CRB 8/5467

Faz Hernández, Armando, 1987-

F297h High-performance elliptic curve cryptography : a SIMD approach to modern curves / Armando Faz Hernández. – Campinas, SP : [s.n.], 2022.

Orientador: Julio César López Hernández. Tese (doutorado) – Universidade Estadual de Campinas, Instituto de Computação.

1. Criptografia. 2. Criptografia de curvas elípticas. 3. Corpos finitos (Álgebra). 4. Aritmética de computador. 5. Algoritmos paralelos. I. López Hernández, Julio César, 1961-. II. Universidade Estadual de Campinas. Instituto de Computação. III. Título.

#### Informações Complementares

Título em outro idioma: Criptografia de curvas elípticas de alto desempenho : uma abordagem SIMD para curvas modernas Palavras-chave em inglês: Cryptography Elliptic curves cryptography Finite fields (Algebra) Computer arithmetic Parallel algorithms Área de concentração: Ciência da Computação Titulação: Doutor em Ciência da Computação Banca examinadora: Julio Cesar Lopez Hernandez Routo Terada Eduardo Moraes de Morais Sara Díaz Cardell Marco Aurélio Amaral Henriques Data de defesa: 23-09-2022 Programa de Pós-Graduação: Ciência da Computação

Identificação e informações acadêmicas do(a) aluno(a)

<sup>-</sup> ORCID do autor: https://orcid.org/0000-0001-5502-8666 - Currículo Lattes do autor: http://lattes.cnpq.br/9952901649594455

Universidade Estadual de Campinas Instituto de Computação

## Armando Faz Hernandez

## High-Performance Elliptic Curve Cryptography: A SIMD Approach to Modern Curves

## Criptografia de Curvas Elípticas de Alto Desempenho: Uma Abordagem SIMD para Curvas Modernas

Comissão Examinadora:

- Prof. Dr. Julio Cesar Lopez Hernandez Instituto de Computação Universidade Estadual de Campinas

- Prof. Dr. Marco Aurélio Amaral Henriques Facultade de Engenheria Elétrica e de Computação Universidade Estadual de Campinas

- Prof. Dr. Routo Terada Instituto de Matemática e Estatística Universidade de São Paulo

- Dr. Eduardo Moraes de Morais Protocol Labs

- Profa. Dra. Sara Díaz Cardell Centro de Matemática, Computação e Cognição Universidade Federal do ABC

A ata da defesa, assinada pelos membros da Comissão Examinadora, consta no SIGA/Sistema de Fluxo de Dissertação/Tese e na Secretaria do Programa da Unidade.

Campinas, 23 de setembro de 2022

Con todo mi cariño para **Ma**, **Pu** y **Ri**.

Enseñarás a volar, pero no volarán tu vuelo. Enseñarás a soñar, pero no soñarán tu sueño. Enseñarás a vivir, pero no vivirán tu vida.

Sin embargo... en cada vuelo, en cada vida, en cada sueño, perdurará siempre la huella del camino enseñado.

## Acknowledgments

This research project was partially supported by the following fellowships and grants.

- **2015-2018** Secure Execution of Cryptographic Algorithms. Grant #2014/50704-7, São Paulo Research Foundation (FAPESP).

- **2013-2016** Software Implementation of Cryptographic Algorithms. Energy-Efficient Security for SoC devices. Intel Strategic Research Alliance. Intel University Research Office.

- **2014** Security and Reliability of Information: Theory and Practice. Grant #2013/25977-7, São Paulo Research Foundation (FAPESP).

- **2011** The São Paulo Advanced School of Cryptography, SP-ASCrypto 2011. Grant #2011/50273-8, São Paulo Research Foundation (FAPESP).

- 2018 ACM SIGSAC. Travel grant. Incheon, South Korea. June, 2018.

- 2013-2017 Latincrypt and ASCrypto committees. Travel grants and stipends. Latincrypt eds. 2014, 2015, and 2017. ASCrypto eds. 2013, 2015, and 2017.

- **2017-2018** Serviço de Apoio ao Estudante (SAE). Bolsa Pesquisa-Empresa.

## Resumo

A criptografia baseada em curvas elípticas fornece métodos eficientes para a criptografia de chave pública. Pesquisa recente tem mostrado a superioridade das curvas de Montgomery e de Edwards sobre as curvas de Weierstrass pois elas precisam de menos operações aritméticas. O uso destas curvas modernas, porém, traz consigo diversos desafios na construção de algoritmos criptográficos deixando em aberto novos alvos de otimizações.

Nosso objetivo principal é propor otimizações algorítmicas e técnicas de implementação para os algoritmos criptográficos baseados em curvas elípticas. Visando acelerar a execução destes algoritmos, nossa abordagem fundamenta-se na utilização extensões ao conjunto de instruções da arquitetura. Além daquelas específicas para a criptografia, nós usamos extensões que seguem o paradigma de cômputo paralelo SIMD (do inglês, *Single Instruction, Multiple Data*). Neste modelo, o processador executa a mesma operação sobre um conjunto de dados de forma paralela. Nós investigamos como aplicar o modelo SIMD na implementação de algoritmos de curvas elípticas.

Como parte de nossas contribuições, projetamos algoritmos paralelos para a aritmética de corpos primos e de curvas elípticas. Projetamos também um algoritmo de multiplicação escalar para calcular P + kQ e uma fórmula otimizada para calcular 3P em curvas de Montgomery. Estes algoritmos encontraram aplicabilidade na criptografia baseada em isogenias. Usando extensões SIMD tais como SSE, AVX e AVX2, desenvolvemos implementações otimizadas dos seguintes algoritmos criptográficos: X25519, X448, SIDH, ECDH, ECDSA, EdDSA e qDSA. Testes de desempenho mostram que essas implementações são mais rápidas do que as implementações existentes no estado da arte.

Nosso estudo confirma que o uso de extensões ao conjunto de instruções da arquitetura é uma ferramenta efetiva para otimizar implementações de algoritmos criptográficos baseados em curvas elípticas. Seja isto um incentivo não somente para aqueles que procuram acelerar os programas em geral, mas também para que os fabricantes de computadores incluam mais extensões avançadas para apoiar a demanda crescente da criptografia.

## Abstract

Cryptography based on elliptic curves is endowed with efficient methods for public-key cryptography. Recent research has shown the superiority of the Montgomery and Edwards curves over the Weierstrass curves as they require fewer arithmetic operations. Using these modern curves has, however, introduced several challenges to the cryptographic algorithm's design, opening up new opportunities for optimization.

Our main objective is to propose algorithmic optimizations and implementation techniques for cryptographic algorithms based on elliptic curves. In order to speed up the execution of these algorithms, our approach relies on the use of extensions to the instruction set architecture. In addition to those specific for cryptography, we use extensions that follow the Single Instruction, Multiple Data (SIMD) parallel computing paradigm. In this model, the processor executes the same operation over a set of data in parallel. We investigated how to apply SIMD to the implementation of elliptic curve algorithms.

As part of our contributions, we design parallel algorithms for prime field and elliptic curve arithmetic. We also design a new three-point ladder algorithm for the scalar multiplication P + kQ, and a faster formula for calculating 3P on Montgomery curves. These algorithms have found applicability in isogeny-based cryptography. Using SIMD extensions such as SSE, AVX, and AVX2, we develop optimized implementations of the following cryptographic algorithms: X25519, X448, SIDH, ECDH, ECDSA, EdDSA, and qDSA. Performance benchmarks show that these implementations are faster than existing implementations in the state of the art.

Our study confirms that using extensions to the instruction set architecture is an effective tool for optimizing implementations of cryptographic algorithms based on elliptic curves. May this be an incentive not only for those seeking to speed up programs in general but also for computer manufacturers to include more advanced extensions that support the increasing demand for cryptography.

## Resumen

La criptografía basada en curvas elípticas está dotada de métodos eficientes para la criptografía de llave pública. Investigaciones recientes han mostrado la superioridad de las curvas de Montgomery y de Edwards sobre las curvas de Weierstrass, pues emplean menos operaciones aritméticas. El uso de estas curvas modernas, en cambio, introduce varios desafíos en el diseño de algoritmos criptográficos y expone nuevos blancos de optimización.

Nuestro objetivo principal es proponer optimizaciones algorítmicas y técnicas de implementación para algoritmos criptográficos basados en curvas elípticas. Para acelerar la ejecución de estos algoritmos, nuestro enfoque se basa en el uso de extensiones al conjunto de instrucciones de la arquitectura. Además de aquellas específicas para la criptografía, nosotros usamos las extensiones que siguen el paradigma de cómputo paralelo SIMD (del inglés, *Single Instruction, Multiple Data*). En este modelo, el procesador ejecuta la misma operación sobre un conjunto de datos de forma paralela. Nosotros investigamos cómo aplicar el modelo SIMD en la implementación de algoritmos de curvas elípticas.

Como parte de nuestras contribuciones, diseñamos algoritmos paralelos para la aritmética de cuerpos primos y de curvas elípticas. Diseñamos también un algoritmo de multiplicación escalar para calcular P + kQ y una fórmula optimizada para calcular 3P en curvas de Montgomery. Estos algoritmos encontraron aplicabilidad en la criptografía basada en isogenias. Usando extensiones SIMD tales como SSE, AVX y AVX2, desarrollamos implementaciones optimizadas de los siguientes algoritmos criptográficos: X25519, X448, SIDH, ECDH, ECDSA, EdDSA y qDSA. Pruebas de rendimiento muestran que estas implementaciones son más rápidas que implementaciones existentes en el estado del arte.

Nuestro estudio confirma que el uso de extensiones al conjunto de instrucciones de la arquitectura es una herramienta efectiva para optimizar implementaciones de algoritmos criptográficos basados en curvas elípticas. Sea esto un incentivo no solamente para aquellos que desean acelerar programas en general, sino también para que los fabricantes de computadoras incluyan más extensiones avanzadas que respalden la demanda creciente de la criptografía.

# List of Figures

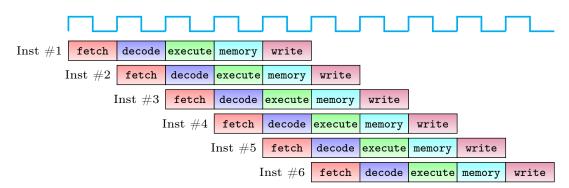

| 2.1.1  | Instruction execution in a five-stage pipeline                      |

|--------|---------------------------------------------------------------------|

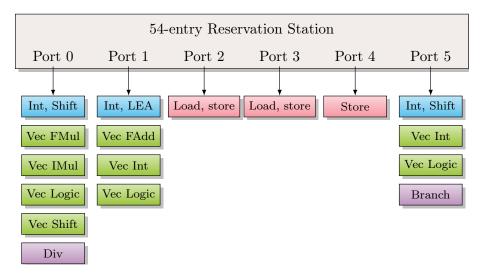

| 2.1.2  | Execution engine of the Sandy Bridge micro-architecture             |

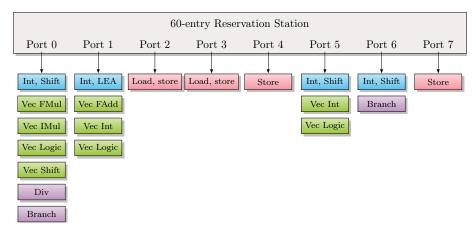

| 2.1.3  | Execution engine of the Haswell micro-architecture                  |

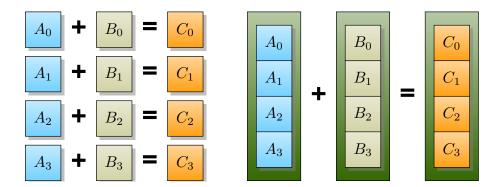

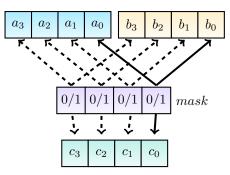

| 2.2.1  | Scalar vs vector processing                                         |

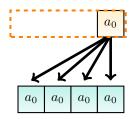

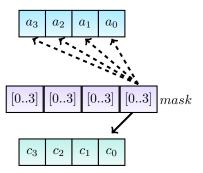

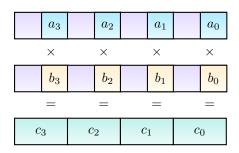

| 2.2.2  | Relevant AVX2 instructions                                          |

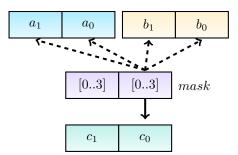

| 2.4.1  | Evolution of vector instructions and hardware extensions            |

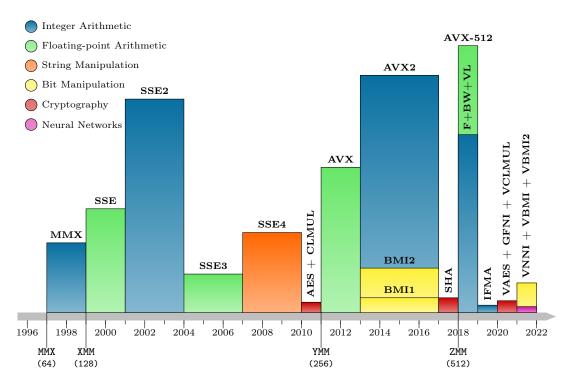

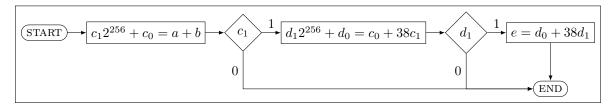

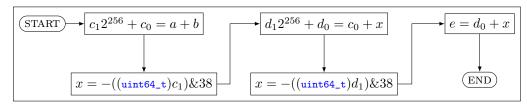

| 3.4.1  | Calculation of additions modulo $p_{25519}$                         |

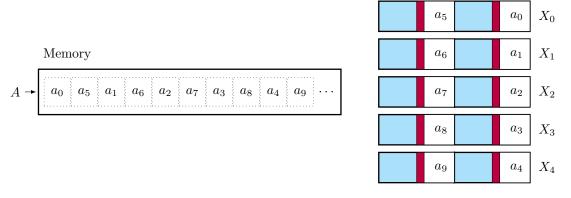

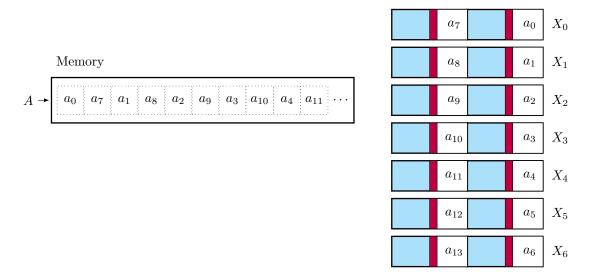

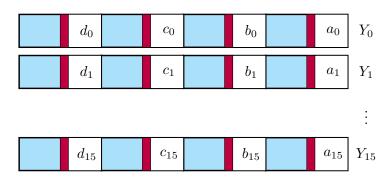

| 3.4.4  | Storing a $\mathbb{F}_{p_{25519}}$ element in 128-bit registers     |

| 3.4.14 | Scheduling of 128-bit instructions for multiplications              |

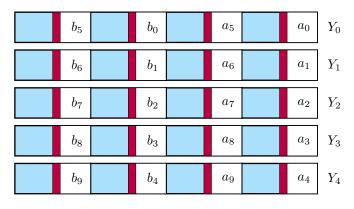

| 3.4.16 | Storing two $\mathbb{F}_{p_{25519}}$ elements in 256-bit registers  |

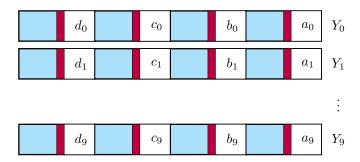

| 3.4.18 | Storing four $\mathbb{F}_{p_{25519}}$ elements in 256-bit registers |

| 3.4.19 | Storing four $\mathbb{F}_{p_{25519}}$ elements in 512-bit registers |

| 3.5.1  | Storing a $\mathbb{F}_{p_{384}}$ element in 128-bit registers       |

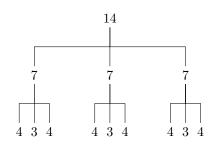

| 3.5.5  | Recursion tree of Karatsuba multiplication for $l = 14. \dots$      |

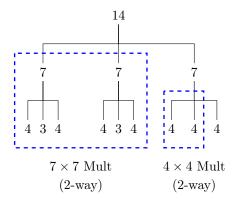

| 3.5.6  | Parallel execution of Karatsuba recursion tree                      |

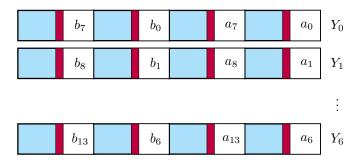

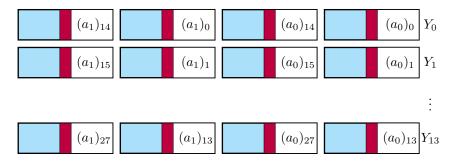

| 3.5.10 | Storing two $\mathbb{F}_{p_{384}}$ elements in 256-bit registers    |

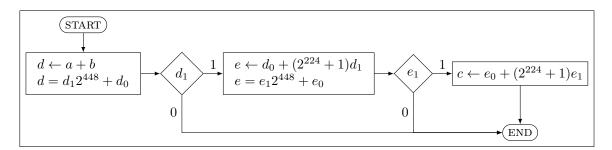

| 3.6.1  | Non-constant-time calculation of additions modulo $p_{448}$         |

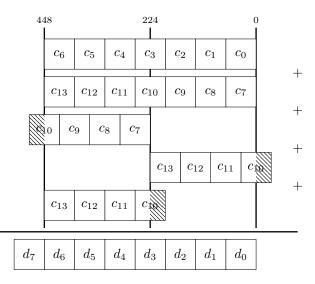

| 3.6.4  | Partial reduction modulo $p_{448}$                                  |

| 3.6.7  | Storing a $\mathbb{F}_{p_{448}}$ element in 128-bit registers       |

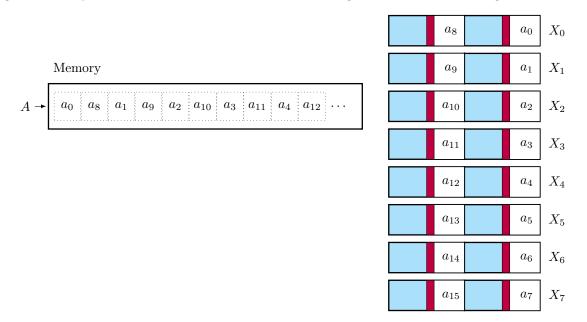

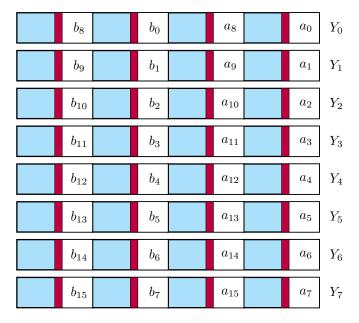

| 3.6.14 | Storing two $\mathbb{F}_{p_{448}}$ elements in 256-bit registers    |

| 3.6.16 | Storing four $\mathbb{F}_{p_{448}}$ elements in 256-bit registers   |

| 3.7.7  | Storing a $\mathbb{F}_{p_{751}}$ element in 128-bit registers       |

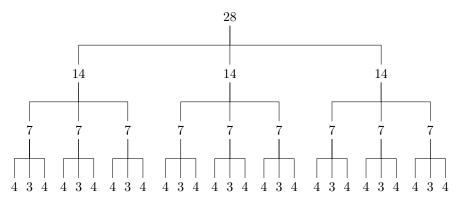

| 3.7.9  | Recursion tree of Karatsuba multiplication for $l = 28$             |

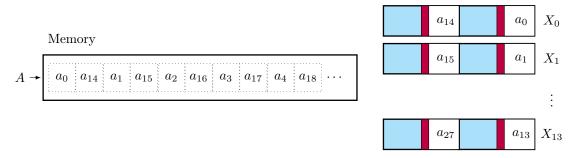

| 3.7.10 | Storing a $\mathbb{F}_{p_{751}^2}$ element in 256-bit registers     |

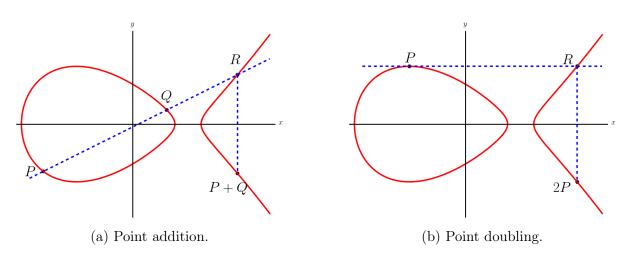

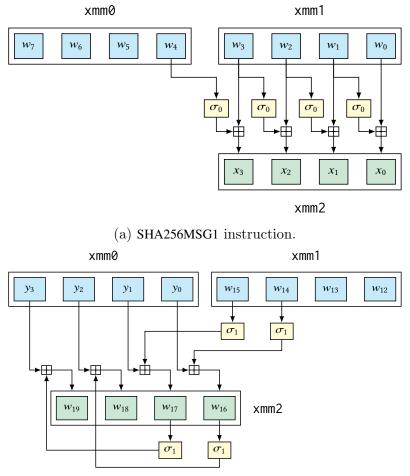

| 4.1.13 | Geometric description of the chord-and-tangent rule                 |

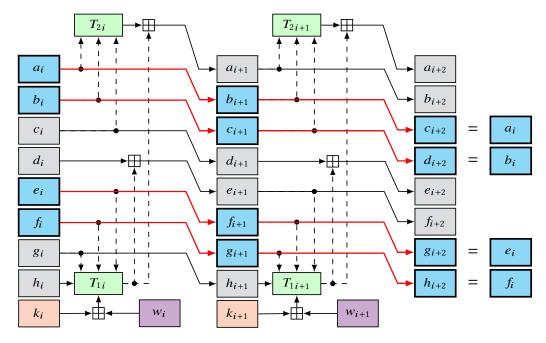

| 4.5.8  | Parallel point addition of twisted Edwards curves by Hisil et al    |

| 4.5.9  | Proposed parallel point addition of twisted Edwards curves          |

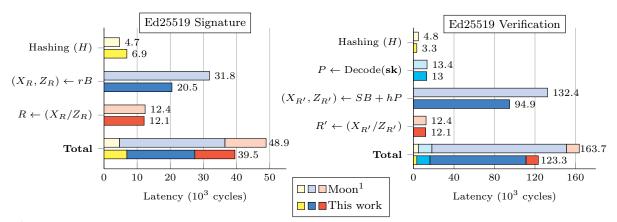

| 5.3.3  | Performance profiling of Ed25519 signature operations               |

| 5.3.4  | Performance profiling of Ed448 signature operations                 |

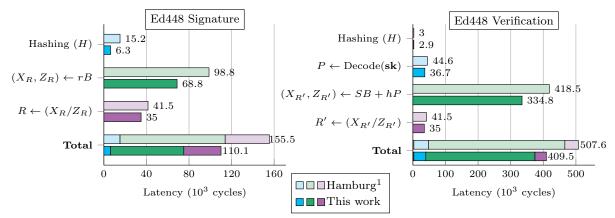

| 5.6.16 | SHA-NI instructions for message schedule phase                      |

| 5.6.21 | Two rounds of the SHA256 algorithm                                  |

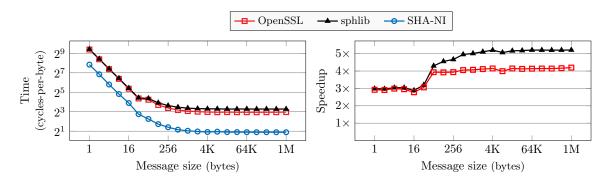

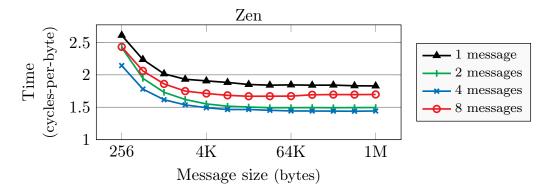

| 5.6.23 | Performance of SHA-256 measured on Zen                              |

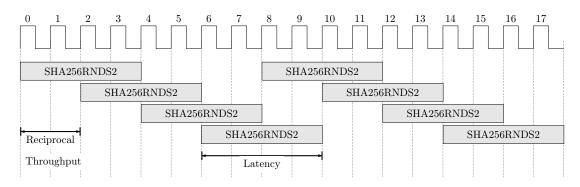

| 5.7.1  | Pipeline execution of SHA256RNDS2 instructions                      |

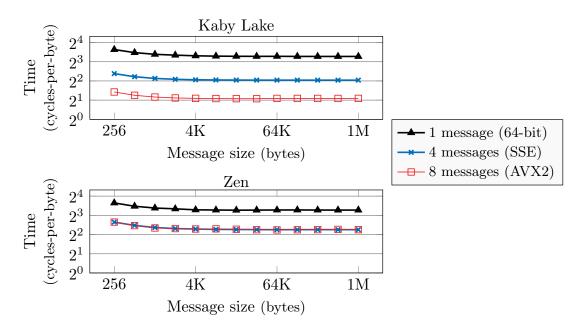

| 5.7.2  | Timings of multiple-message SHA-256 hashing                         |

| 5.7.3  | Timings of pipelined multiple-message SHA-256 hashing               |

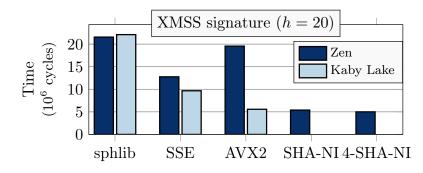

| 5.7.5  | Performance comparison of XMSS                                      |

## List of Tables

| $1.1.1 \\ 1.5.1$ | Comparison of the bit-length of keys of cryptosystems                                                             | 23<br>31 |

|------------------|-------------------------------------------------------------------------------------------------------------------|----------|

| 2.1.4            | Comparison of hardware optimizations                                                                              | 42       |

| $3.2.8 \\ 3.4.2$ | Comparison of machine representations of $n$ -bit integers                                                        |          |

| 3.4.15           | Time in clock cycles of $\mathbb{F}_{p_{25519}}$ operations measured on Skylake                                   | 88       |

| 3.4.17           | Time in clock cycles of two-way $\mathbb{F}_{p_{25519}}$ operations measured on Skylake.                          | 90       |

| 3.4.20           | Time in clock cycles of four-way $\mathbb{F}_{p_{25519}}$ operations measured on Skylake                          | 92       |

| 3.5.11           | Time in clock cycles of $\mathbb{F}_{p_{384}}$ operations measured on Skylake                                     | 100      |

| 3.6.3            | Instruction counts of 448-bit integer multiplication.                                                             | 102      |

| 3.6.13           | Time in clock cycles of $\mathbb{F}_{p_{448}}$ operations measured on Skylake                                     | 108      |

| 3.6.15           | Time in clock cycles of two-way $\mathbb{F}_{p_{448}}$ operations measured on Skylake                             | 110      |

| 3.6.17           | Time in clock cycles of four-way $\mathbb{F}_{p_{448}}$ operations measured on Skylake.                           |          |

| 3.7.6            | Instruction counts of reduction modulo $p_{751}$ .                                                                |          |

| 3.7.15           | Time in clock cycles of $\mathbb{F}_{p_{751}^2}$ operations measured on Skylake                                   | 121      |

| 4.3.2            | Operation counts of point addition for Weierstrass curves                                                         |          |

| 4.3.9            | Operation counts of parallel $\mathbb{F}_q$ -complete formulas                                                    |          |

| 4.4.18           | Operation counts of parallel algorithms for Montgomery ladder step                                                | 153      |

| 4.4.22           | Operation counts of scalar multiplication on the $x$ -line                                                        |          |

| 4.4.25           | Operation counts of $\mathbf{x}(P+kQ)$ on the <i>x</i> -line                                                      | 158      |

| 4.4.35           | Operation counts of point tripling on the $x$ -line                                                               | 161      |

| 4.5.12           | Time in clock cycles of point addition on a twisted Edwards curve                                                 | 165      |

| 4.5.19           | Operation counts of fixed-point multiplication on the edwards25519 curve.                                         | 168      |

| 5.1.1            | Suite B of cryptographic algorithms.                                                                              |          |

| 5.1.6            | Timings of ECDH and ECDSA using P-384                                                                             |          |

| 5.2.5            | Timings of X25519 shared secret. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |          |

| 5.2.6            | Timings of X448 shared secret                                                                                     | 180      |

| 5.2.7            | Timings of the key generation phase of X25519 and X448                                                            |          |

| 5.2.8            | Timings of the Diffie-Hellman protocol at the 128-bit security level                                              | 182      |

| 5.3.5            | Timings of Ed25519 and Ed448                                                                                      |          |

| 5.4.13           | Timings of qDSA using the right-to-left fixed-point ladder                                                        | 195      |

| 5.4.14           | Timings of qDSA operations                                                                                        | 195      |

| 5.4.15           | Timings of qDSA and other digital signature schemes                                                               | 196      |

| 5.5.4            | Timings of $\mathbf{x}(P + [k]Q)$ for SIDH-751                                                                    |          |

| 5.5.5            | Timings of SIDH-751                                                                                               | 201      |

| 5.7.4            | Timings of XMSS and $XMSS^{MT}$ measured on Zen                                                                   | 213      |

|                  | -                                                                                                                 |          |

# List of Algorithms

| 2.3.1  | The AES encryption algorithm                                                                                      |

|--------|-------------------------------------------------------------------------------------------------------------------|

| 3.1.6  | Integer addition using full adder circuit                                                                         |

| 3.1.8  | Integer subtraction using full subtractor circuit                                                                 |

| 3.1.14 | Montgomery's REDC algorithm                                                                                       |

| 3.2.2  | Obtaining the radix- $2^w$ representation of an integer                                                           |

| 3.2.4  | Obtaining the generalized polynomial representation of an integer 67                                              |

| 3.2.12 | Integer Addition using Polynomial Representation                                                                  |

| 3.2.13 | Integer Multiplication using Polynomial Representation (operand scan-                                             |

|        | ning method). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 69                 |

| 3.2.14 | Integer Addition using Redundant Representation                                                                   |

| 3.2.23 | Integer Multiplication using Redundant Representation                                                             |

| 3.2.26 | Karatsuba Algorithm for Integer Multiplication using Redundant Repre-                                             |

|        | sentation. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ |

| 3.2.28 | Digit Size Reduction (sequential)                                                                                 |

| 3.2.29 | Digit Size Reduction (parallel).                                                                                  |

| 3.4.12 | Adaptation of Mastrovito's Algorithm for Prime Field Multiplication using                                         |

|        | Redundant Representation.                                                                                         |

| 3.5.7  | Reduction modulo $p_{384}$                                                                                        |

| 3.6.2  | Constant-time implementation of additions modulo $p_{448}$                                                        |

| 3.6.10 | Karatsuba multiplication merged with reduction modulo $p_{448}$                                                   |

| 3.7.1  | Montgomery's REDC algorithm in radix- $2^w$                                                                       |

| 3.7.5  | Montgomery's REDC tuned for $p = 2^a b - 1$ in radix $2^w$                                                        |

| 3.7.13 | Multiplication on $\mathbb{F}_{p^2}$                                                                              |

| 3.7.14 | Squaring on $\mathbb{F}_{p^2}$                                                                                    |

| 4.2.1  | Left-to-Right Binary Algorithm for Scalar Multiplication                                                          |

| 4.2.2  | Right-to-Left Binary Algorithm for Scalar Multiplication.                                                         |

| 4.2.3  | Fixed-Window Algorithm for Scalar Multiplication.                                                                 |

| 4.2.4  | Conversion of Integers to $\omega$ -NAF Representation.                                                           |

| 4.2.5  | The $\omega$ -NAF Algorithm for Scalar Multiplication.                                                            |

| 4.2.6  | Conversion of Integers to Signed-Digit Representation                                                             |

| 4.2.7  | Regular Signed-Digit Algorithm for Scalar Multiplication                                                          |

| 4.2.8  | Montgomery Ladder for Scalar Multiplication.                                                                      |

| 4.2.9  | Joye Ladder for Scalar Multiplication                                                                             |

| 4.2.10 | CSWAP-based Montgomery Ladder Algorithm for Scalar Multiplication. 135                                            |

| 4.2.11 | CMOV-based Montgomery Ladder Algorithm for Scalar Multiplication 135                                              |

| 4.2.12 | CSWAP-based Joye Ladder Algorithm for Scalar Multiplication                                                       |

| 4.2.13 | CSWAP Implemented with Logic Arithmetic                                                                           |

| 4.2.14 | CMOV Implemented with Logic Arithmetic.                                                                           |

| 1.4.17 | chieve impromented with Logic Antonneoles.                                                                        |

| 4.2.15 | Interleaved Algorithm for Multiple-Point Multiplication                                         |

|--------|-------------------------------------------------------------------------------------------------|

| 4.2.16 | Interleaved Algorithm with $\omega$ -NAF for Double-Point Multiplication 139                    |

| 4.3.3  | Two-way $\mathbb{F}_q$ -Complete Point Addition on $E/\mathbb{F}_q$ : $y^2 = x^3 + Ax + B$ 142  |

| 4.3.4  | Two-way $\mathbb{F}_q$ -Complete Point Addition on $E/\mathbb{F}_q$ : $y^2 = x^3 - 3x + B$ 142  |

| 4.3.5  | Two-way $\mathbb{F}_q$ -Complete Point Doubling on $E/\mathbb{F}_q$ : $y^2 = x^3 + Ax + B$ 143  |

| 4.3.6  | Two-way $\mathbb{F}_q$ -Complete Point Doubling on $E/\mathbb{F}_q$ : $y^2 = x^3 - 3x + B$ 143  |

| 4.3.7  | Four-way $\mathbb{F}_q$ -Complete Point Addition on $E/\mathbb{F}_q$ : $y^2 = x^3 + Ax + B$ 143 |

| 4.3.8  | Four-way $\mathbb{F}_q$ -Complete Point Doubling on $E/\mathbb{F}_q$ : $y^2 = x^3 + Ax + B$ 144 |

| 4.4.11 | Montgomery Ladder Algorithm for Scalar Multiplication on the $x$ -Line. 148                     |

| 4.4.14 | Recovering the y-Coordinate of a Point on a Montgomery Curve $150$                              |

| 4.4.15 | Scalar Multiplication of Points on a Montgomery Curve                                           |

| 4.4.16 | Two-way Parallel Algorithm for Montgomery Ladder Step                                           |

| 4.4.17 | Four-way Parallel Algorithm for Montgomery Ladder Step                                          |

| 4.4.19 | Right-to-Left Ladder Algorithm for Scalar Multiplication on the $x$ -Line 154                   |

| 4.4.21 | Right-to-Left Ladder Algorithm for Fixed-Point Multiplication on the $x$ -                      |

|        | Line                                                                                            |

| 4.4.23 | Left-to-Right Three-Point Ladder Algorithm for $\mathbf{x}(P+kQ)$                               |

| 4.4.24 | Right-to-Left Three-Point Ladder Algorithm for $\mathbf{x}(P+kQ)$                               |

| 4.4.26 | Right-to-Left Three-Point Ladder Algorithm for $\mathbf{x}(P + kQ)$ with Fixed-                 |

|        | Points                                                                                          |

| 4.4.34 | Point Tripling on the <i>x</i> -Line                                                            |

| 4.5.10 | Two-way Point Addition for Twisted Edwards Curves with $a = -1$ 165                             |

| 4.5.11 | Four-way Point Addition for Twisted Edwards Curves with $a = -1$ 166                            |

| 4.5.16 | Conversion of Integers to Signed Digits                                                         |

| 5.4.12 | Unequivocal Verification Procedure for qDSA.                                                    |

| 5.6.11 | Update Function for SHA-256                                                                     |

| 5.6.22 | SHA-256 Update Implemented with SHA-NI                                                          |

|        | · ·                                                                                             |

## Contents

| Fo       | Foreword 1            |                                                      |           |  |

|----------|-----------------------|------------------------------------------------------|-----------|--|

| Pı       | reface                | e                                                    | 19        |  |

| 1        | $\operatorname{Intr}$ | roduction                                            | 20        |  |

|          | 1.1                   | Cryptography                                         | 20        |  |

|          |                       | 1.1.1 Symmetric-Key Cryptography                     | 21        |  |

|          |                       | 1.1.2 Public-Key Cryptography                        | 21        |  |

|          |                       | 1.1.3 Elliptic Curve Cryptography                    | 22        |  |

|          | 1.2                   | Cryptographic Engineering                            | 24        |  |

|          |                       | 1.2.1 Security of Implementations                    | 24        |  |

|          |                       | 1.2.2 Efficiency of Implementations                  | 25        |  |

|          |                       | 1.2.3 Shifting to Modern Elliptic Curves             | 25        |  |

|          | 1.3                   | Related Works                                        | 26        |  |

|          |                       | 1.3.1 Algorithmic Optimizations                      | 26        |  |

|          |                       | 1.3.2 Software Implementations of Elliptic Curves    | 27        |  |

|          |                       | 1.3.3 Implementations using Hardware Extensions      | 28        |  |

|          | 1.4                   | Research Problem                                     | 29        |  |

|          |                       | 1.4.1 Motivation                                     | 29        |  |

|          |                       | 1.4.2 Problem Statement                              | 30        |  |

|          | 1.5                   | Aims and Scope                                       | 30        |  |

|          |                       | 1.5.1 Aims                                           | 30        |  |

|          |                       | 1.5.2 Scope                                          | 30        |  |

|          | 1.6                   | Contributions                                        | 32        |  |

|          |                       | 1.6.1 Publications                                   | 32        |  |

|          |                       | 1.6.2 Software Libraries                             | 34        |  |

|          | 1.7                   | Outline                                              | 35        |  |

| •        | ът                    |                                                      |           |  |

| <b>2</b> |                       | dern Computer Architectures                          | <b>36</b> |  |

|          | 2.1                   | Optimizations in Computer Architectures              | 36        |  |

|          |                       | 2.1.1 Pipeline Execution                             | 37        |  |

|          |                       | 2.1.2 Superscalar Processors                         |           |  |

|          |                       | 2.1.3 Simultaneous Multi-Threading                   | 39<br>40  |  |

|          |                       | 2.1.4 Parallel Computing                             | 40        |  |

|          | 0.0                   | 2.1.5 Comparison of Optimizations                    | 42        |  |

|          | 2.2                   | SIMD Vector Units                                    | 43        |  |

|          | 0.0                   | 2.2.1 Vector Instructions of the x86-64 Architecture | 44        |  |

|          | 2.3                   | Extensions for Cryptography                          | 48        |  |

|          |                       | 2.3.1 The AES New Instructions                       | 48        |  |

|          |      | 2.3.2    | The Carry-Less Multiplier                             | 49  |

|----------|------|----------|-------------------------------------------------------|-----|

|          |      | 2.3.3 N  | Multi-Precision Integer Arithmetic                    | 49  |

|          |      | 2.3.4    | The SHA New Instructions                              | 51  |

|          |      |          | Vectorized AES and Galois Field Extensions            |     |

|          | 2.4  | Evolutio | on of Hardware Extensions                             | 52  |

|          | 2.5  | Chapter  | Summary                                               | 52  |

| 3        | Prii | me Field | l Arithmetic                                          | 54  |

|          | 3.1  | Algebra  | ic Structures                                         | 54  |

|          |      | 3.1.1    | The Ring of Integers                                  | 56  |

|          |      | 3.1.2 I  | Prime Fields                                          | 58  |

|          |      | 3.1.3 H  | Extension Fields                                      | 63  |

|          | 3.2  | Operatio | ons over Prime Field Elements                         | 65  |

|          |      | 3.2.1 N  | Machine Representation of Integers                    | 65  |

|          |      | 3.2.2 (  | Operations using Polynomial Representation            | 68  |

|          |      | 3.2.3 (  | Operations using a Redundant Representation           | 70  |

|          | 3.3  |          | Calculation of Arithmetic Operations                  |     |

|          | 3.4  |          | etic on $\operatorname{GF}(2^{255} - 19)$             |     |

|          |      |          | Polynomial Representation                             |     |

|          |      | 3.4.2 I  | Redundant Representation                              | 81  |

|          |      | 3.4.3    | Two-way Operations                                    | 89  |

|          |      |          | Four-way Operations                                   |     |

|          | 3.5  | Arithme  | etic on $GF(2^{384} - 2^{128} - 2^{96} + 2^{32} - 1)$ | 92  |

|          |      | 3.5.1 I  | Redundant Representation                              | 93  |

|          |      |          | Two-way Operations                                    |     |

|          |      |          | Performance Benchmark                                 |     |

|          | 3.6  | Arithme  | etic on $GF(2^{448} - 2^{224} - 1)$                   | 100 |

|          |      |          | Polynomial Representation                             |     |

|          |      | 3.6.2 I  | Redundant Representation                              | 104 |

|          |      | 3.6.3    | Two-way Operations                                    | 109 |

|          |      |          | Four-way Operations                                   |     |

|          | 3.7  | Arithme  | etic on $\operatorname{GF}((2^a b - 1)^2)$            | 111 |

|          |      | 3.7.1 I  | Improvements on the Reduction Modulo $p = 2^a b - 1$  | 111 |

|          |      | 3.7.2 I  | Redundant Representation                              | 117 |

|          |      | 3.7.3    | Two-way Operations for the Quadratic Extension        | 119 |

|          |      | 3.7.4 I  | Performance Benchmark                                 | 121 |

|          | 3.8  | Chapter  | Summary                                               | 122 |

| <b>4</b> | Ari  | thmetic  | of Elliptic Curves                                    | 123 |

|          | 4.1  | Backgro  | und                                                   | 123 |

|          |      | 4.1.1 H  | Elliptic Curves                                       | 123 |

|          |      | 4.1.2    | The Group of Rational Points                          | 126 |

|          |      | 4.1.3 H  | Elliptic Curve Discrete Logarithm Problem             | 128 |

|          | 4.2  | 0        | ms for Scalar Multiplication                          |     |

|          |      | 4.2.1 I  | Basic Algorithms                                      | 129 |

|          |      | 4.2.2 A  | Algorithms with Regular Execution Pattern             | 131 |

|          |      | 4.2.3 I  | Ladder Algorithms                                     | 133 |

|          |      | 4.2.4    | Special Cases                                         | 136 |

|          | 4.3  | Arithme  | etic of Weierstrass Curves                            | 139 |

|          |     | 4.3.1 Point Addition Formulas                                                                                                                                                        | 39 |

|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          |     | 4.3.2 Parallel Complete Addition Formulas                                                                                                                                            | 11 |

|          | 4.4 | Arithmetic of Montgomery Curves                                                                                                                                                      | 14 |

|          |     | 4.4.1 Montgomery Curves                                                                                                                                                              | 15 |

|          |     | 4.4.2 The x-Line Variety $\ldots \ldots \ldots$                      | 16 |

|          |     | 4.4.3 Parallel Montgomery Ladder Step                                                                                                                                                | 50 |

|          |     | 4.4.4 A Review of Right-To-Left Algorithms                                                                                                                                           | 52 |

|          |     | 4.4.5 A New Three-Point Ladder Algorithm                                                                                                                                             | 55 |

|          |     | 4.4.6 An Optimized Point Tripling Formula                                                                                                                                            | 59 |

|          | 4.5 | Arithmetic of Twisted Edwards Curves                                                                                                                                                 | 31 |

|          |     | 4.5.1 Twisted Edwards Curves                                                                                                                                                         | 32 |

|          |     | 4.5.2 Parallel Point Addition                                                                                                                                                        | 33 |

|          |     | 4.5.3 Fixed-Point Multiplication                                                                                                                                                     | 36 |

|          | 4.6 | Chapter Summary $\ldots \ldots \ldots$                               |    |

| <b>5</b> | C   | otographic Algorithms and Protocols 17                                                                                                                                               | 70 |

| Э        | 5.1 | Implementation of ECDH and ECDSA with P-384                                                                                                                                          |    |

|          | 0.1 | 5.1.1 Review of Standard Elliptic Curves                                                                                                                                             |    |

|          |     | 5.1.2 Implementation Details                                                                                                                                                         |    |

|          |     | 5.1.3 Performance Benchmark and Comparison                                                                                                                                           |    |

|          | 5.2 | Implementation of X25519 and X448                                                                                                                                                    |    |

|          | 0.2 | 5.2.1 Review of Diffie-Hellman Protocol on the <i>x</i> -Line                                                                                                                        |    |

|          |     | 5.2.1 Interview of Dime-Heiman 1 fotocol on the $x$ -Line $\ldots$ $\ldots$ $\ldots$ $17$<br>5.2.2 Implementation Details $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $17$ |    |

|          |     | 5.2.2 Performance Benchmark and Comparison                                                                                                                                           |    |

|          | 5.3 | -                                                                                                                                                                                    |    |

|          | 0.0 | Implementation of Ed25519 and Ed448185.3.1Review of Edwards Digital Signature Algorithm18                                                                                            |    |

|          |     |                                                                                                                                                                                      |    |

|          |     | 1                                                                                                                                                                                    |    |

|          | F 4 | 5.3.3 Performance Benchmark and Comparison                                                                                                                                           |    |

|          | 5.4 | Implementation of qDSA using Curve25519                                                                                                                                              |    |

|          |     | 5.4.1 Review of the Quotient Digital Signature Algorithm                                                                                                                             |    |

|          |     | 5.4.2 Implementation Details                                                                                                                                                         |    |

|          |     | 5.4.3 Unequivocal Verification Methods                                                                                                                                               |    |

|          | F F | 5.4.4 Performance Benchmark and Comparison                                                                                                                                           |    |

|          | 5.5 | Implementation of SIDH-751                                                                                                                                                           |    |

|          |     | 5.5.1 Review of Supersingular Isogeny Diffie-Hellman                                                                                                                                 |    |

|          |     | 5.5.2 Implementation Details                                                                                                                                                         |    |

|          | FC  | 5.5.3 Performance Benchmark and Comparison                                                                                                                                           |    |

|          | 5.6 | Implementation of SHA-256 $\dots \dots \dots$                                        |    |

|          |     | 5.6.1 The SHA-256 Algorithm                                                                                                                                                          |    |

|          |     | 5.6.2 Implementation Details                                                                                                                                                         |    |

|          |     | 5.6.3 Performance Benchmark and Comparison                                                                                                                                           |    |

|          | 5.7 | Implementation of XMSS and $XMSS^{MT}$                                                                                                                                               |    |

|          |     | 5.7.1 Review of Hash-based Signatures                                                                                                                                                |    |

|          |     | 5.7.2 Implementation Details                                                                                                                                                         |    |

|          |     | 5.7.3 Performance Benchmark and Comparison                                                                                                                                           |    |

|          | 5.8 | Chapter Summary                                                                                                                                                                      | 4  |

| 6            | Con        | clusio                                                                          | ns                              | 215                                                                       |

|--------------|------------|---------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------|

|              | 6.1        | Conclu                                                                          | ıding Remarks                   | 215                                                                       |

|              | 6.2        | Retros                                                                          | $\mathbf{pective}$              | 216                                                                       |

|              |            | 6.2.1                                                                           | Specialized Literature          | 216                                                                       |

|              |            | 6.2.2                                                                           | Programming Languages           | 216                                                                       |

|              |            | 6.2.3                                                                           | Usage of AVX2                   | 217                                                                       |

|              |            | 6.2.4                                                                           | New Instructions                | 218                                                                       |

|              | 6.3        | Summ                                                                            | ary of Contributions            | 219                                                                       |

|              |            | 6.3.1                                                                           | Algorithmic Optimizations       | 219                                                                       |

|              |            | 6.3.2                                                                           | Implementation Techniques       | 220                                                                       |

|              | 6.4        | Future                                                                          | e Work                          | 221                                                                       |

| Bi           | bliog      | graphy                                                                          |                                 | 222                                                                       |

|              |            |                                                                                 |                                 |                                                                           |

| $\mathbf{A}$ | Res        | earch ]                                                                         | Production                      | 250                                                                       |

| A            | Res<br>A.1 |                                                                                 | Production<br>al Articles       |                                                                           |

| Α            |            |                                                                                 | al Articles                     | 250                                                                       |

| A            |            | Journa                                                                          | al Articles                     | $250 \\ 250$                                                              |

| A            |            | Journa<br>A.1.1<br>A.1.2                                                        | Al Articles                     | 250<br>250<br>251                                                         |

| Α            | A.1        | Journa<br>A.1.1<br>A.1.2                                                        | Al Articles                     | 250<br>250<br>251<br>251<br>251                                           |

| Α            | A.1        | Journa<br>A.1.1<br>A.1.2<br>Public                                              | A Faster Implementation of SIDH | 250<br>250<br>251<br>251<br>251                                           |

| Α            | A.1        | Journa<br>A.1.1<br>A.1.2<br>Public<br>A.2.1                                     | Al Articles                     | 250<br>250<br>251<br>251<br>251<br>251<br>252                             |

| Α            | A.1        | Journa<br>A.1.1<br>A.1.2<br>Public<br>A.2.1<br>A.2.2                            | A Faster Implementation of SIDH | 250<br>250<br>251<br>251<br>251<br>252<br>252<br>253                      |

| A            | A.1        | Journa<br>A.1.1<br>A.1.2<br>Public<br>A.2.1<br>A.2.2<br>A.2.3                   | A Faster Implementation of SIDH | 250<br>250<br>251<br>251<br>251<br>252<br>253<br>253<br>253               |

| A            | A.1        | Journa<br>A.1.1<br>A.1.2<br>Public<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4          | Al Articles                     | 250<br>250<br>251<br>251<br>251<br>252<br>253<br>253<br>253               |

| Α            | A.1        | Journa<br>A.1.1<br>A.1.2<br>Public<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5 | A Faster Implementation of SIDH | 250<br>250<br>251<br>251<br>251<br>252<br>253<br>253<br>253<br>254<br>255 |

## Foreword

Armando's journey towards obtaining his doctoral degree was long, and I am delighted to have witnessed it from a close distance for most of it. It started during the end of my doctoral degree at UNICAMP and continued after we both left Brazil in search of better opportunities.

Our collaboration began in 2011 when we worked on using the unpronounceable PCLMULQDQ carryless multiplier instruction to speed up software implementations of binary elliptic curves. At the time, Armando was doing his Master's degree in Mexico under the supervision of Francisco Rodríguez-Henríquez, Ph.D., who became a great common friend not long after. I can still remember the excitement of finally seeing binary fields as a first-class citizen in modern vector instruction sets —supported natively by a main computer manufacturer— and then the disappointment of benchmarking the instruction at 14 cycles.

That was our first CHES paper, accepted at the premier conference of our still-growing field. There were other collaborations after that, some of which are included in this thesis. We extended our techniques to the Koblitz curves for LATINCRYPT 2012, got a joint paper accepted to SPACE 2017, and worked on a short course for SBSeg 2015. Writing short course chapters is a tradition in Brazil, as a way for more senior researchers to introduce the field to newcomers. I find it sometimes a joyless and laborious work, but sharing the burden with Armando and co-authors made it better somehow. Meanwhile, the throughput of PCLMULQDQ decreased to just 1 cycle!

Armando has come a long way, and it shows clearly in his thesis. He matured from a graduate student to an experienced cryptographic engineer with an impressive publication record. His contributions in the thesis set speed records for the implementation of many standardized curves used in production for protocols critical to modern society, such as SSH and TLS. The breadth of his work went past beyond Elliptic Curve Cryptography to also impact the emerging field of quantum-safe isogeny-based cryptography, which is, unfortunately, facing some troubled teenage years currently.

I hope the reader can have as much fun reading the thesis, as I had enjoyed collaborating with Armando and witnessing his every new achievement. Since we share our brilliant doctoral advisor Julio López, Ph.D., I guess this makes Armando my academic younger brother. Here he is for many more speed records to come!

> Diego F. Aranha, Ph.D. Associate Professor, Aarhus University

## Preface

From my perspective, I feel I started this project a while back ago, even before I joined UNICAMP. One good day, I was a part of a crowd of international students attending the Advanced School of Cryptography (ASCrypto'11) in Atibaia, São Paulo. This event certainly pushed me forward in the right direction. Elliptic curves and bilinear pairings were the trending topics in my circles. To be honest, I was tempted to get involved in cryptanalysis, but I found lots of affinity with UNICAMP's research projects, its faculty staff, and the mighty future that was looming. A couple of emails later and a quick conversation with Prof. Julio Lopez in Santiago, Chile was more than enough to decide to pack my stuff and land in Campinas in 2013 to become a doctoral student.

During my PhD, I have received support in many different ways. So, I would like to express my gratitude to Prof. Julio Lopez, who advises me not only academically but also in daily life. I remember many good conversations that left me with meaningful things. He always showed eagerness to support my research, and I appreciate his patience and trust during the bad days. Needless to say, we share a particular interest in binary curves.

I also want to highlight the leadership and expertise of Prof. Ricardo Dahab, who has fostered a solid cryptography community. Likewise, I admire the tenacity of Diego Aranha, we worked close while he was at UNICAMP. To Francisco Rodríguez, for the support given when attending Latincrypt events. Also, I want to mention the kindness of Fabio Tagnin, David Ott, and Rafael Misoczki, who followed in part this project. To Nick Sullivan, who gives me valuable advice.

I would like to thank my committee members, all my professors, administrative staff, the international office, libraries, dining and other campus facilities of the University of Campinas for the great labor done at the service of national and foreign students. Similar acknowledgments, to the state of São Paulo and the entire Brazilian nation.

I feel fortunate to meet amazing people and colleagues who were partakers of many adventures on my journey. I appreciate and value the friendship of Amanda, Ana, Carlos, Citlali, David, Eduardo, Francisco, Hayato, Israel, Jadisha, Junior, Karina, Kiiro, Leonara, Manuel, Marcelo, Marleny, Patrick, Rafael, Roberto, Sheila, Thomaz, and everyone that I missed mentioning.

Todo mi aprecio a mi querida familia; a Carmen, Armando y Susana. Porque gracias a su ayuda incondicional y motivación hoy podemos celebrar juntos este nuevo logro.

This thesis summarizes lots of efforts for optimizing elliptic curve cryptography. Participating in this project was satisfactory, with no time to get bored as new and clever ideas appear every other day. Parts of this document were written in sunny Campinas and hilly San Francisco. Hope this research helps others to solve problems, and encourage people to continue researching the points that remain unexplored.

# Chapter 1 Introduction

The simplest communication model involves two honest participants, called Alice and Bob, who want to interchange messages through a public communication channel. There is also a participant, known as Eve, who can eavesdrop the messages transmitted through the channel. In this context:

> How can Alice and Bob communicate confidentially even in the presence of Eve?

This is a central problem in the field of cryptography.

## 1.1 Cryptography

Cryptography is a discipline that studies how to encode information so it remains secret and protected from adversaries. More formally, *cryptography* is the scientific study of techniques for securing digital information, transactions, and distributed computations [170].

One solution cryptography provides to the above problem is data encryption. An encryption algorithm converts a message, also known as *plaintext*, into a *ciphertext*. Alice encrypts a message and send the ciphertext to Bob. Once Bob receives the ciphertext, he uses a decryption algorithm that recovers the original message from the ciphertext. Eve never has access to the original message because only the ciphertext is in transit. So Alice and Bob can communicate confidentially.

An issue of the procedure described above is that the algorithms must be kept secret. If Eve knows the encryption or decryption algorithms, she would be able to participate in the conversation. Hiding the algorithms is, however, not always possible or even practical. A better approach is to shift the secrecy requirements from the algorithms to the secrecy of an additional data, referred to as *keys*. Thus, the encryption and decryption algorithms take a key as an additional input making possible to publicly disclose the algorithms used. If Alice and Bob maintain the key in secrecy, they can interchange encrypted messages without Eve being able to read them.

It is evident that the initial problem becomes harder as adding more details to its description. In the following sections, we incrementally introduce some other issues that allow us to motivate the actual research problem addressed in this thesis. We then present our approach to solve it and show the findings of our study. Let's begin.

#### 1.1.1 Symmetric-Key Cryptography

In the description above, we showed a system that enables two entities to communicate confidentially through an insecure channel. More formally, a *cryptosystem* consists of the encryption and decryption algorithms together with the set of all possible plaintexts, ciphertexts, and keys. It is said a cryptosystem offers a *security level of*  $\lambda$  *bits* if the bestknown attack that breaks it requires a computational effort of  $O(2^{\lambda})$  operations. Examples of breaking a cryptosystem includes methods that systematically find the secret key or recover the plaintext from a ciphertext without knowledge of the key. The security level of a cryptosystem is strongly related to the size of the key space.

In data encryption algorithms, only those with knowledge of the key are able to encrypt and to decrypt messages. In general, there is no restriction on using different keys for encryption and decryption provided that one key can be easily obtained from the other. Algorithms that use the same key for encrypting and decrypting messages are known as *symmetric-key encryption* algorithms, which are studied by a branch of cryptography known as *symmetric-key cryptography*.

The put in practice of symmetric-key encryption raises some issues concerning to the management of keys. Issues on the operational side include a secure way to distribute keys among the participants. For example, rotation of keys must be performed every time a participant abandons a group of communication. There are also issues regarding the storage of keys. If one-to-one secret communication is needed for a group of n participants, there is required to store  $n^2$  keys securely, which can be cumbersome if the group keeps growing. A trusted key distribution center addresses this issue for fixed-sized groups. Unfortunately, it does not scale to groups with an arbitrary number of participants.

The symmetric-key cryptography assumes that Alice and Bob *share* a secret key, which they use to interchange encrypted messages. One way to agree on the key is, for example, by having an in-person secret conversation; but, in practice, this is not always possible. For this reason, Alice and Bob require a secure way to agree on a secret key through the public communication channel. This requirement of symmetric-key cryptography is not easy to accomplish; at least, not until the discovery of a revolutionary idea that solves this problem and that introduced a new paradigm for cryptography.

#### 1.1.2 Public-Key Cryptography

In 1976, Diffie and Hellman [87], and independently Merkle [192], shown new ideas that led to the origin of a new branch of cryptography called *public-key cryptography*. Specifically, they proposed the use of two personal keys: one of them is made publicly available, and the other key is in the private possession of its owner.

The first algorithm of public-key cryptography is the Diffie-Hellman protocol [87]. This protocol allows Alice and Bob to agree on a shared secret through an insecure communication channel. Thus, Alice and Bob can generate a shared key that they use as a secret key in a symmetric-key encryption algorithm. The combination of these two techniques enables confidential communication between participants located remotely.

Another breakthrough in public-key cryptography is the separation of the capabilities of the keys. In public-key data encryption, Alice uses Bob's public key to encrypt a message sending the ciphertext through the channel. Upon receiving the ciphertext, Bob uses his private key to decrypt it and recovers the message. Unlike symmetric-key encryption, a public key is used only for encryption and a private key only for decryption. This imbalance in the capabilities of keys motivates the name of *asymmetric* cryptography when referring to the public-key cryptography [149, 190, 256].

A fundamental requirement for this asymmetry to work is that it must be computationally infeasible to obtain the private key from the public key. A way to ensure this relies on the assumption that one-way functions exist. A function is *one-way* if it is easy to compute but hard to invert. Although no proof is known for the existence of one-way functions, the hardness of some mathematical problems serves to base one-way functions. A concrete example is the integer factoring problem in number theory. It is easy to calculate the product of two prime integers, but finding the factors from their product is widely believed to be hard.

There exists a well-known cryptosystem based on the hardness of integer factoring. In 1977, Rivest, Shamir, and Adleman [232] proposed a public-key encryption algorithm known as RSA. Let p and q be two primes and n = pq, choose an integer e > 1 such that  $gcd(e, \phi(n)) = 1$ , where  $\phi(n) = (p - 1)(q - 1)$ ; then there exists a unique d such that  $ed \equiv 1 \pmod{\phi(n)}$ . Now, given (n, e) as the public key, it is hard to find the private key d without the knowledge of  $\phi(n)$ . The encryption of a message m is performed as  $c = m^e \mod n$ , whereas decryption is  $m = c^d \mod n$ . The RSA problem [233] is to recover the message given a ciphertext and the public key. This problem becomes easy if d or the factorization of n is known. Currently, no polynomial time algorithms for integer factoring are known; the best ones have sub-exponential time complexity on the size of the primes. The RSA assumption supports the security of public-key encryption and digital signature schemes massively used in digital communications.

ElGamal [92] proposed the use of the discrete logarithm problem in group theory for basing a one-way function. Given a group with generator g and assuming an efficientlycomputable group law, it is easy to calculate group exponentiation, i.e., given g and an integer k to calculate  $h = g^k$ . The opposite calculation is known as the *discrete logarithm problem* (DLP), which is to find the integer k given g and arbitrary element h such that  $h = g^k$ . The hardness of the DLP depends on the choice of the group. For example, in the multiplicative group of the integers modulo a prime, the best-known algorithms have sub-exponential time-complexity on the size of the group order. Hence, it is desirable to use a group with a strong DLP and an efficient group law. A group with these properties is found in the theory of elliptic curves.

### 1.1.3 Elliptic Curve Cryptography

In 1985, Koblitz [171] and Miller [194] independently proposed a way to use elliptic curves in public-key cryptography leading to the *elliptic curve cryptography* (ECC). Specifically, they noted that elliptic curves defined over finite fields allow instantiating groups with a hard discrete logarithm problem. The main advantage of elliptic curve-based cryptosystems is the use of shorter key sizes and more efficient operations than previous cryptosystems such as RSA. Elliptic curves have a special mathematical structure that allows instantiating a group. The points lying on an elliptic curve are the group elements, and the group law takes two points P and Q on the curve and calculates their addition P + Q, which is also a point on the curve. Analogously to the group exponentiation, the scalar multiplication operation multiplies a point P by an integer k, which abbreviates the repeated application of the group law on P to itself k - 1 times, and the resulting point is denoted as kP.

As in the general case, one can base a one-way function from this group. Given a generator P of the group and an integer k, it is easy to calculate kP. On the other hand, given two points P and Q, finding an integer k such that Q = kP is believed to be a hard problem, which is known as the *elliptic curve discrete logarithm problem* (ECDLP). The best-known algorithm for solving ECDLP is the Pollard's rho algorithm [226], which has exponential time-complexity on the size of the group order.

Elliptic curve cryptography is efficient with regard to the size of keys. The complexity of the ECDLP has an advantage over the DLP on the multiplicative group of integers modulo a prime. By fixing the effort required for solving these problems, the order of the group is smaller in the case of elliptic curve groups. In practice, this translates on shorter key sizes for equivalent security levels. Table 1.1.1 lists estimates of the key sizes of some symmetric-key and public-key cryptosystems. It is clear the advantage of elliptic curve-based algorithms, specially when moving to higher security levels.

| Security Level | Symmetric-key Algorithm | Pu         | ıblic-key Alş | gorithm   |

|----------------|-------------------------|------------|---------------|-----------|

| (bits)         | AES                     | RSA        | DL-based      | ECC-based |

| 128            | 128                     | 3,072      | 3,072         | 256       |

| 192            | 192                     | 7,680      | 7,680         | 384       |

| 256            | 256                     | $15,\!360$ | 15,360        | 512       |

Table 1.1.1: Comparison of the bit-length of keys of cryptosystems.

Although elliptic curves are the object of study of number theory and algebraic geometry, their use in cryptography attracted so much attention introducing a number of applications. For example, Lenstra [179] used elliptic curves in integer factoring algorithms, a problem that Montgomery [196] also studied giving significant contributions used in contemporary algorithms. Some other applications of elliptic curves include digital signature schemes, protocols for key agreement and key encapsulation, public-key encryption, pairing-based cryptography, zero-knowledge proof systems, and multiparty computation systems. More recently, elliptic curves also found a place in the portfolio of quantum-resistant algorithms leading to the *isogeny-based cryptography*, which relies on the mathematical relations between elliptic curves to base a one-way function. In summary, elliptic curve cryptography has positioned as an efficient way for supporting public-key cryptography in practice.

## 1.2 Cryptographic Engineering

The fundamentals of cryptography are as relevant as their put in practice. For this reason, special attention must be given to the *cryptographic engineering*, which focuses on the application and practical aspects related to the use of cryptography and its implementation under real-world constraints [105].

The security of implementations is a chief goal to pursue. Translating mathematical formulations into machine instructions is not a straightforward task because it is prone to introduce not only errors, but also security vulnerabilities. Although security always prevails over other goals, it is not the only factor when using a system in practice as some other engineering constraints should be considered too. In certain situations such as scaling up a system or when the computational resources are limited, the computational efficiency becomes a relevant factor.

Security and efficiency are goals often in compromise. For example, suppose an application requires to perform group exponentiation by a secret exponent. One may be tempted to use the fastest algorithm, however, the algorithm could be expose a time variation that depends on the exponent; thus, revealing the secret. In this situation, the fastest algorithm is not always suitable for its direct use in cryptography.

The following sections focus on the implementation of elliptic curve cryptography. We describe some aspects regarding the security and the efficiency of software implementations. We also describe a recent initiative that motivates the need for new elliptic curves.

### 1.2.1 Security of Implementations

The security of a system is as strong as its weakest link. Breaking a cryptographic algorithm is by far the attacker's target, but breaking its implementation is an easier one. A special class of implementation-specific attacks are the *side-channel attacks* [173]. In this scenario, the attacker tries to learn some secret data while the computer is running. To do so, the attacker measures some physical variables of the computer environment and correlates these measurements with the data processed. The attacker's success highly depends on the behavior of the hardware and the software implementation during execution.

Side-channel attacks are a first-class concern when implementing cryptography. Although hardware implementations are more susceptible to these attacks, software implementations can also be vulnerable as has been exemplified in these works [4,57,178]. For this reason, protecting software implementations against side-channel attacks is mandatory to prevent the leakage of secret information. There exist several types of side-channel attacks such as timings attacks, cache-memory attacks, and power analysis attacks.

One type of side-channel attacks are the *timing attacks*. For instance, assume a program executes a time-consuming operation only when a determined bit of a secret key is set, otherwise it performs a faster operation. A timing attack leverages this situation. So an attacker that observes variations in the running time of a program can correlate a longer execution with the bits of the key that are set, thus, learning the secret information. A conventional countermeasure against timing attacks is to ensure the program follows a regular execution pattern when processing secret data, and to ensure that the latency of operations is independent of the secret values. This programming pattern, also known as a *constant-time execution*, is key for developing secure implementations.

Other well-known techniques exist for protecting implementations against side-channel attacks. For example, secret data must not remain in memory for a long time, only when needed; and after its use, it must be wiped out. Also programs must avoid using secret data for performing bifurcations and to use secret indexes for accessing memory, these patterns in programs are often the target of cache-memory attacks. Hence, the development of cryptographic algorithms must consider all these threats to protect implementations. As the attacks become more powerful, looking for new methods and techniques to protect implementations is an active research topic.

#### **1.2.2** Efficiency of Implementations

Efficiency is a relevant factor in the implementation of algorithms. Generally, *efficiency* is regarded as the proper utilization of the computational resources to accomplish a task without a waste of time and effort. Usually, efficiency is linked to high performance, but the vast diversity of devices and computer architectures brings a variety of metrics for determining the efficiency of implementations.

Latency is the amount of time that an operation takes to be executed. Commonly the unit of latency is the second. Nonetheless, when measuring fine-grained operations, such as machine instructions, the number of clock cycles is used instead. An advantage of using clock cycles is that it allows to made comparisons between computers that have a similar architecture but that run at different clock frequencies. A metric closely related to latency is the *throughput*, which is the number of operations performed by a unit of time, and is usually reported as operations-per-second (or instructions-per-cycle, if measuring the throughput of instructions of a program). Both metrics can be used as indicators of the performance of an implementation.

*Memory footprint* is another metric used for efficiency that indicates the amount of memory required to perform a task. The memory footprint of a program is often an issue in systems with memory limitations, such as in embedded devices. This is not the case in commodity computer architectures. Depending on the execution environment, memory footprint becomes an influential factor for the efficiency of an implementation.

More recently, the energy consumption of computers has become a concern regarding efficiency. This concern is not particular to the increasing use of battery-powered devices but it also applies to large data centers supporting Internet applications. On the hardware side, modern computer architectures allow the processor to run at a lower power level reducing their energy consumption. However, there is still investigation needed to make programs consume less power, and more tooling for measuring energy consumption.

#### 1.2.3 Shifting to Modern Elliptic Curves

Since their introduction to cryptography, the research on elliptic curves has focused on finding better algorithms, optimizing curve parameters, and proposing improvements for both hardware and software implementations. In 1999, a set of elliptic curves was recommended for their standardization [200]. Their use for performing cryptographic operations was endorsed by international organizations such as the American National Standards Institute (ANSI) [8,9], the Institute of Electrical and Electronics Engineers (IEEE) [155], the National Institute of Standards and Technology (NIST) [204], among others. Sometime later, the standardized curves became the subject of controversy after the discovery of trapdoors in a standardized algorithm based on elliptic curves for pseudorandom number generation [249].

The research community responded with an active avalanche of proposals that improve over the standard elliptic curves. Firstly, the parameter generation process of new elliptic curves should not be biased, so all parameters must be chosen through rigid and explicit arguments. A line of research promotes the use of faster elliptic curve forms such as the Montgomery, Hessian, and (twisted) Edwards curves. Also due to the recent efforts on solving DLP over binary fields [166, 241], several proposals have a preference for defining curves over finite fields of large characteristic rather than over small characteristic fields.

Several proposals appeared intending to improve security and efficiency. The Safe-Curves [36] project summarizes some of them. The following is a non-exhaustive list of these proposals:

- Curve25519 [23]